### **Infrastructure Technology Institute**

SAFETEA-LU Project 2010—2012

# FINAL REPORT

# Piezoresistive Strain Sensors and Multiplexed Arrays for Transportation Infrastructures

Principal Investigator:

# Yonggang Huang

Joseph Cummings Professor of Civil and Environmental Engineering and Mechanical Engineering

> October 2012 Northwestern University Evanston, Illinois

### **DISCLAIMER**

The contents of this report reflect the views of the authors, who are responsible for the facts and the accuracy of the information presented herein. This document is disseminated under the sponsorship of the Department of Transportation University Transportation Centers Program, in the interest of information exchange. The U.S. Government assumes no liability for the contents or use thereof.

### Piezoresistive Strain Sensors and Multiplexed Arrays for Transportation Infrastructures

Principal Investigator: Professor Yonggang Huang

During Year 5 of SAFETEA-LU, ITI researcher Professor Yonggang Huang, an expert in the science of stretchable and flexible electronics, collaborated with researchers at University of Illinois to engineer stretchable and flexible piezoresistive strain sensors and multiplexed arrays for advanced structure health monitoring of transportation infrastructures.

The piezoresistive strain sensors and multiplexed arrays cover a finite area of the surface of transportation infrastructures, and provide the spatial distribution of strain. These sensors and multiplexed arrays are particularly suitable for curvilinear surfaces with sharp corners, which usually have stress or strain concentrations and require accurate sensing. In addition, the gauge factor of piezoresistive strain sensors is more than two orders of magnitude higher than conventional strain sensors. They can measure much more accurately the maximum strain in the critical components (e.g., sharp corners, complex shapes) of the transportation infrastructure experiences.

Prior to SAFETEA-LU Year 5, Professor Huang's research focused on flexible silicon-based strain sensors. The research and support in Year 5 enabled him and his collaborators to develop stretchable sensors, and particularly in multiplexed arrays.

We have applied the stretchable and flexible electronic technology to sensors for structural health monitoring of transportation infrastructures. The large, flexible and high-sensitivity sensor arrays enable rapid, accurate and robust measurement of strain distribution on any surface. This may lead to accurate damage assessment of transportation infrastructures (e.g., bridges, highways) and prediction of service life, which is important to the highway structures portion of National Strategy of Surface Transportation Research identified by USDOT research goals.

We have developed materials, integration strategies, mechanical models and system demonstrations of distributed networks of piezoresistive strain sensors based on ultrathin single-crystalline silicon membranes on thin plastic substrates (i.e. polyimide). Such systems offer high sensitivity (i.e. piezoresistive coefficient or gauge factor) of single-crystalline silicon while providing lightweight construction and mechanical flexibility. By using Wheatstone bridge configurations for the sensors and coupling them to multiplexing diodes, this technology can be scaled to large-area, integrated monitors with spatial mapping capabilities that also naturally provide compensation for variations in temperature. They overcome the limitations of current sensors, and thereby opening up new opportunities for structural health monitoring of transportation infrastructures.

Figure 1. Illustration of the process flow for piezoresistive strain sensors and multiplexed arrays.

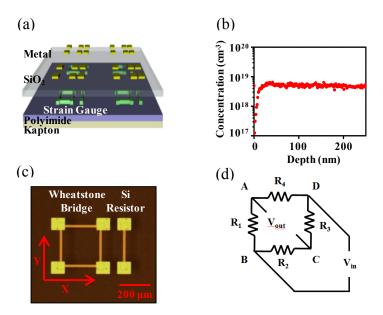

The procedures to fabricate piezoresistive strain sensors build on concepts demonstrated for flexible electronics, in which ultrathin silicon ribbons or membranes (which we refer to as microstructured silicon, or s-Si) are derived from bulk wafers, or silicon-oninsulator (SOI) substrates, and then assembled using printing-like techniques onto thin sheets of plastic [1]-[3]. A major advantage of these piezoresistive strain sensors is that their gauge factors (based on silicon) are about two orders of magnitude higher than the currently used strain sensors, and are much more sensitive to strain. We have used SOI (Soitec, unibond with 300-nm top p-type Si layer with resistivity of 14-22  $\Omega$ -cm) to create devices illustrated schematically in exploded view format in Fig. 1a. The process begins by defining p- and n- doped regions in s-Si via impurity diffusion procedures. Increasing the doping concentration improves the quality of ohmic contacts and reduces the temperature dependence of the resistance, but at the expense of reductions in the piezoresistance factor (i.e. strain sensitivity or gauge factor) [4]-[5]. With a boron concentration of ~5 x 10<sup>18</sup>/cm<sup>3</sup>, the silicon is sufficiently doped to provide a good ohmic contact. Furthermore, at this concentration, the temperature dependence (i.e. temperature coefficient of resistance or TCR) is reduced by factor of  $\sim 5X$  [4], while the longitudinal piezoresistance factor is maintained to ~75% [5] of its value at concentrations of 1 x 10<sup>16</sup>/cm<sup>3</sup>. By precisely controlling the diffusion temperature and duration, approximately uniform concentrations of boron ( $\sim$ 5 x 10<sup>18</sup>/cm<sup>3</sup>) is achieved throughout the thickness (i.e. 300nm) of the silicon used here, as illustrated in Fig. 2b. We have used a simple strain gauge geometry, in which a layer of SiO<sub>2</sub> (deposited by plasma-enhanced chemical vapor deposition) and metallization of Cr/Au (deposited by electron beam evaporation)

serves as interlayer dielectric (ILD) and electrodes, respectively. Figure 2c provides optical images of a strain gauge that uses a Wheatstone bridge (WB) design with four separate s-Si resistors, as well as a separate, isolated s-Si resistor, all on a polyimide substrate (Dupont; Kapton(R) 100E film, 75 µm thickness). The circuit schematic is illustrated in Fig. 1d; power is applied to nodes A and C, while output voltages is measured between B and D.

For the design and fabrication of piezoresistive strain sensors shown in Fig. 1, we have conducted both mechanical and electrical modeling and simulations. Both finite element analysis and circuit analysis have been conducted. Modeling and simulations results have been validated by the experimental results for a single sensor. The validated models and simulation tools have been used to optimally design large strain sensor arrays, particularly multiplexed arrays that can cover a representative portion of surfaces of transportation infrastructures; can be wrapped conformally on complex surfaces of transportation infrastructures; and have high strain sensitivity, which is about two orders more sensitive than any of the current strain sensors.

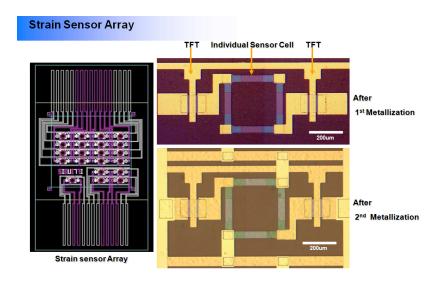

Figure 2. Illustration of the design of strain sensor arrays.

Figure 2 shows the design of multiplexed sensor arrays, which provides a robust approach to fabricate piezoresistive strain sensors and multiplexed arrays. Its stretchable and flexible design enables its placement on any complex surface. The fabrication technique is particularly suitable for large sensor arrays because the process always involves simultaneous fabrication of a large batch of sensors/devices. Thin film transistors (TFT) in Fig. 2 response fast enough to input bias such that there is no signal drift from the sensor array. The Wheastone bridge itself in the sensor array is very durable, and survives sustain 10,000 cycles of bending.

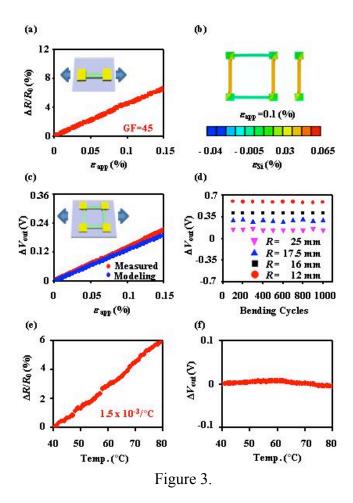

Uniaxial tensile strain applied along the lengths of resistor devices reveals their strain-induced changes in resistance. Figure 3a shows a representative set of data from a device that incorporates a strip of silicon with dimensions of  $20 \times 200 \,\mu\text{m}^2$ ; the inset provides a schematic illustration. The resistance varies linearly with tensile strain throughout this range; the effective gauge factor (*GF*) of this heterogeneous system is ~43 derived by

$$GF = \frac{R}{R_{\text{app}}} \tag{1}$$

where  $\varepsilon_{app}$  is the applied strain onto the polyimide substrate.

Since the mechanical properties (e.g. moduli) of the silicon and the polyimide substrate differ by nearly a factor of one hundred, the GF measured in this manner does not directly yield the value for the s-Si. Finite Element Method (FEM) gives distributions of strain that can then be used to determine intrinsic GF values (i.e.  $GF_{Si}$ ). Figure 3b presents a plot of the calculated strain on the top layer of the silicon resistor and the WB strain gauge for an applied tensile strain of 0.1% along the vertical direction. The FEM results indicate that the strain in the silicon is approximately 0.045% when a strain of 0.1% is applied to the polyimide substrate, for a device that has overall dimensions (i.e. silicon and surrounding polyimide) of 30 x 1 mm. The value of  $GF_{Si}$  can be calculated by

$$GF_{Si} = GF \xrightarrow{\text{app}} Si$$

(2)

For GF=43 at an applied strain  $\varepsilon$ =0.1%, the true strain in the silicon  $\varepsilon_{Si}$ =0.045%, such that  $GF_{Si}$  to found to be ~97. The intrinsic gauge factor of [110] Si can be calculated analytically by the following equation [17]

$$GF_{Si[110]} = \neq {}_{Si[110]}E_{Si[110]} = 0.8 71.8 10^{-11} 168 10^9 = 96.49$$

(3)

where  $\alpha$  is a correction coefficient accounting for different doping concentration,  $\pi_{Si[110]}$  is the piezoresistive coefficient and E represents the Young's modulus. This calculated  $GF_{Si}$  value is in excellent agreement with our experiment and modeling result.

Figure 3c shows the change in output voltage of a WB strain gauge under  $\pm 3$  V input bias as a function of applied uniaxial tensile strain (inset, Fig. 3c). To model the voltage, we use the well-known equation

$$\frac{V_{out}}{V} = \frac{R_4}{R_3 + R_4} \quad \frac{R_2}{R_1 + R_2} \tag{4}$$

where R denotes the resistance of each bridge (i.e. each s-Si resistor) and can be calculated by

$$R = R_0 (1 + GF) \tag{5}$$

where  $\varepsilon$  is the applied strain and  $R_0$  is the initial resistance of each bridge. For samples under uniaxial tension,  $\varepsilon$  is the applied tensile strain; for sample under pure bending (i.e. bent around a cylindrical tube),

$$=\frac{h}{2a} \tag{6}$$

where h is the sample sheet thickness and r is the bending radius. Simulation based on Eqs. (4) ~ (5) result agrees well with measured results, as illustrated in Fig. 3c.

The mechanical fatigue properties of these devices are important to understand, due to the mechanically brittle nature of the silicon, and to the stresses that concentrate at the interface between the silicon and the underlying polyimide. For this purpose, we meausured the change in output voltage for many cycles of bending to various radii. The results in Fig. 3d shows that the changes in output voltages do not vary in any appreciable way to bending radii from 25mm to 12mm with up to 1000 cycles. These data suggest mechanically robust construction and stable operation. Another parameter of practical concern is sensitivity to variations in temperature. Figure 3e presents the resistance of a us-Si resistor as a function of temperature. The extracted temperature coefficient of resistance (TCR) of  $1.5 \times 10^{-3}$  oC is comparable to literature values for p-type silicon with  $\sim 10^{18}$ /cm<sup>3</sup> dopant concentration. The value reduces to  $7.0 \times 10^{-3}$ /°C, perhaps due to the carrier repopulation in the valence band, for a device bent to a radius of 25 mm. For strain gauges in WB configurations, same TCR associated with four us-Si resistors yields minimal temperature effect in the unstrained condition, although the temperature can affect the device performance in the strained state. This behavior can be seen clearly in the data of Fig. 3f.

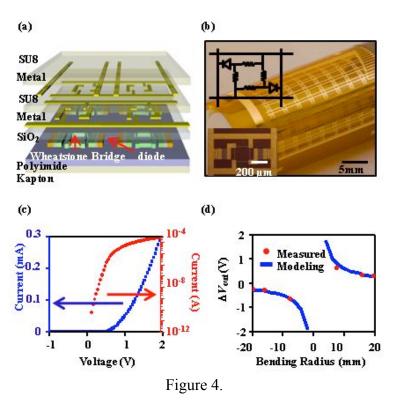

Electrically integrating these strain gauges with PN diodes can yield distributed networks of sensors with multiplexed readout, for large area applications. For multiplexing, we chose PN diodes over transistors, due to their relative simplicity in construction and operation. Figure 4a shows the layout of such a system where two PN diodes connected at the output nodes of each WB. In this structure, every row of WBs shares a single input bias line. Each WB has two differential outputs, and each column also shares a line, which is connected to the cathodes of the PN diodes in that column. All the WBs share an additional -3V bias line. Multiplexing operates by applying +3V to the input bias line of each row, in turn, while holding the bias of all the other rows at -3V. This biasing condition causes the diodes in all columns except the ones on the currently 'on' row to be reverse biased. As a result, the output from each column only has a contribution from the single WB that is biased on in that column. Figure 4b shows the optical image of the array and the inset provides an image of a single unit cell. Figure 4c presents the electrical characteristic of integrated PN diodes. The off current is 85 nA at a reverse bias of 1 V; the value passes 0 A at a forward bias of 0.1 V.

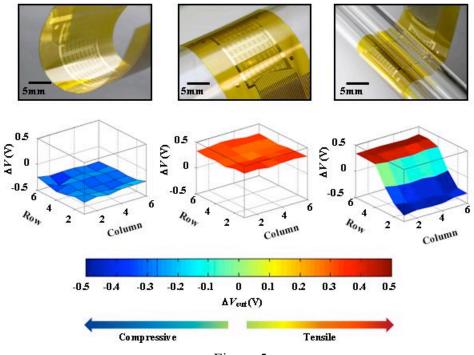

Figure 4d shows the operation of a multiplexed, 6x6 array of sensors, measured at various bending radii. The red dots indicates the average output value from the array; the blue lines represent output voltage derived from Eq. (1). The sign of the output voltage depends on the stress condition (i.e. tensile or compressive) as shown on the graph where positive and negative bending radii, corresponding to tensile and compressive states, respectively, are indicated. Figure 5 shows the operation of the array, operated in a spatial mapping mode, under tensile and compressive, and a combination of these two conditions, achieved by different bending configurations.

Figure 5.

This project presents a flexible, strain mapping technology and multiplexing strategy that uses printed micro/nanostructures for single crystalline silicon for gauges and PN diodes on plastic substrates. Mechanical and electrical measurements show good stability and high sensitivity, well suited for many applications in structural health monitoring and others. Extensions of these ideas can be used with stretchable or curvilinear substrates, to address demanding requirements in strain mapping in transportation infrastructures.

#### References

- [1] J.-H. Ahn, H.-S. Kim, K. J. Lee, S. Jeon, S. J. Kang, Y. Sun, R. G. Nuzzo, and J. A. Rogers, "Heterogeneous three-dimensional electronics by use of printed semiconductor nanomaterials," *Science*, vol. 314, pp. 1754-1757, 2006.

- [2] J.-H. Ahn, H.-S. Kim, E. Menard, K.J. Lee, Z. Zhu, D.-H. Kim, R. G. Nuzzo, J. A. Rogers, "Bendable integrated circuits on plastic substrates by use of printed ribbons of single-crystalline silicon, *Appl. Phys. Lett*, vol. 90, p. 213501, 2007.

- [3] D. -H. Kim, W. M. Choi, J. -H. Ahn, H. -S. Kim, J. Song, Y. Huang, Z. Liu, C. Lu, C. G. Koh, and J. A. Rogers, "Complementary logic gates and ring oscillators on plastic substrates by use of printed ribbons of single-crystalline silicon," *IEEE. Dev. Let*, vol. 29, 2008.

- [4] P. Norton, and J. Brandt, "Temperature coefficient of resistance for p- and n-type silicon," *Solid-State Electronics*, vol. 21, pp. 969-974, 1978.

- [5] R. Hull, "Properties of crystalline silicon," *The institution of Engineering and Technology*, pp. 425-427, London, 1999.

#### **DISCLAIMER**

The contents of this report reflect the views of the authors, who are responsible for the facts and the accuracy of the information presented herein. This document is disseminated under the sponsorship of the Department of Transportation University Transportation Centers Program, in the interest of information exchange. The U.S. Government assumes no liability for the contents or use thereof.